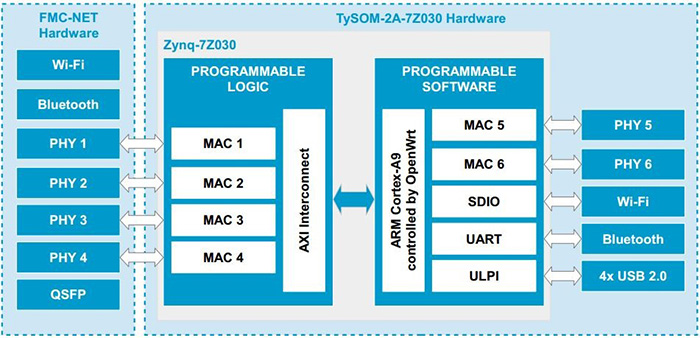

AntSDR E200 - Gigabit Ethernet Connecté SDR avec Xilinx Zynq SoC FPGA, Prend en Charge la Portée de 70 MHz à 6 GHz (Crowdfunding) - AliExpress

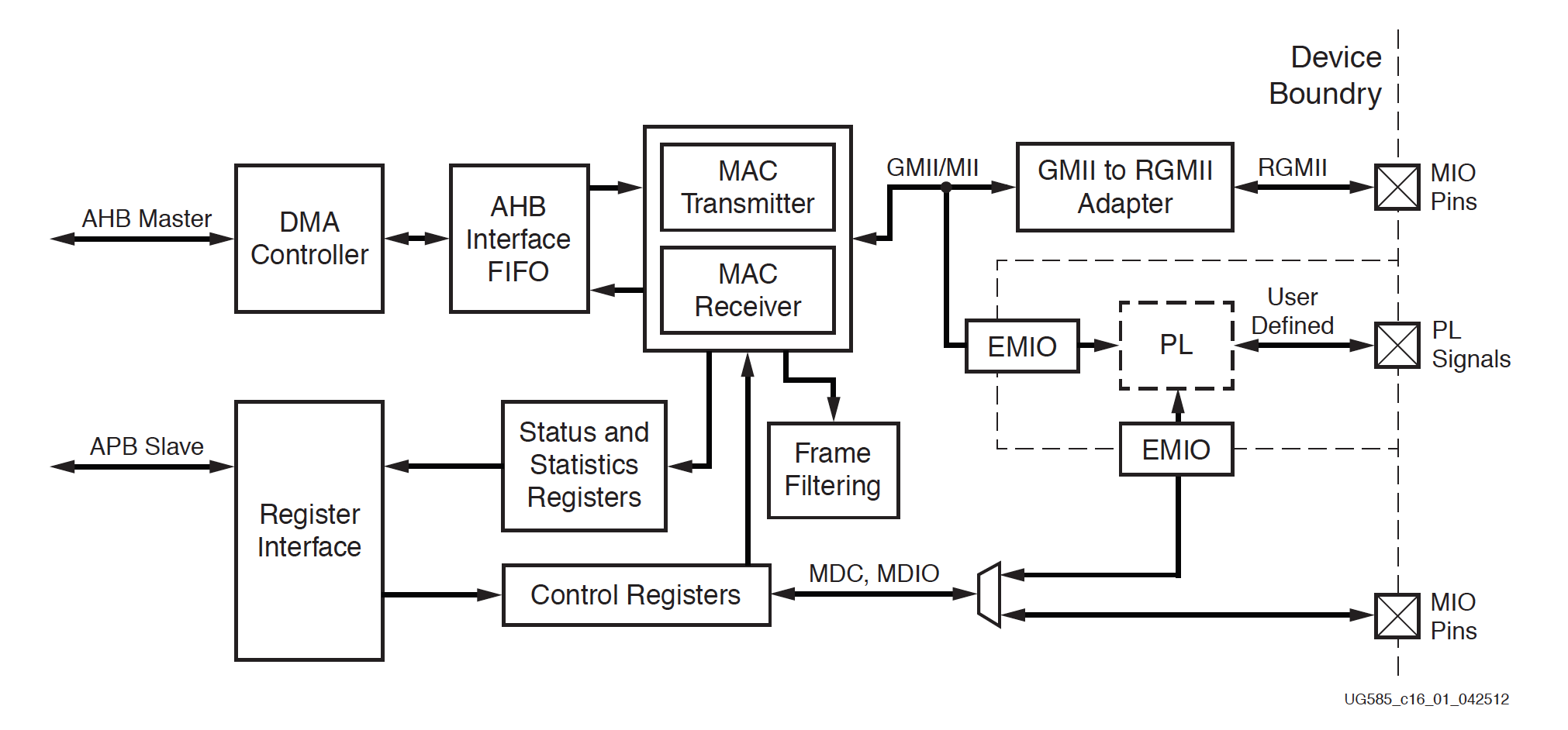

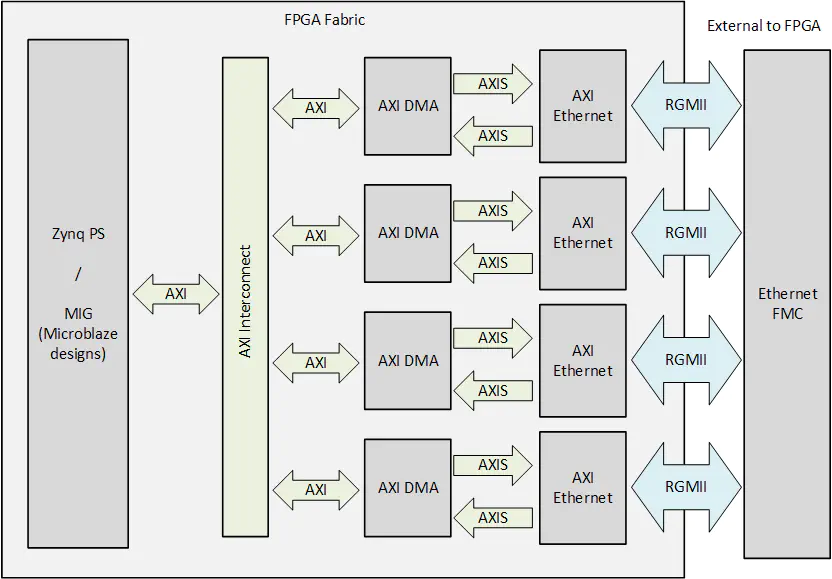

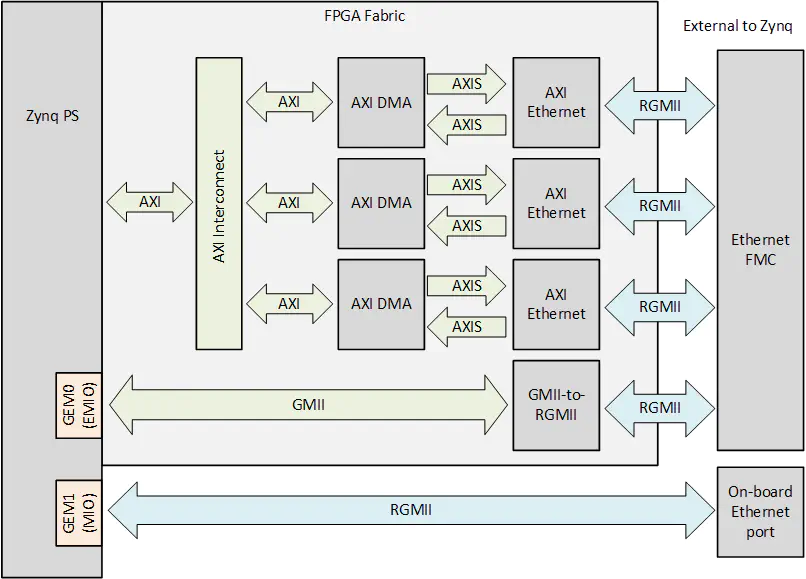

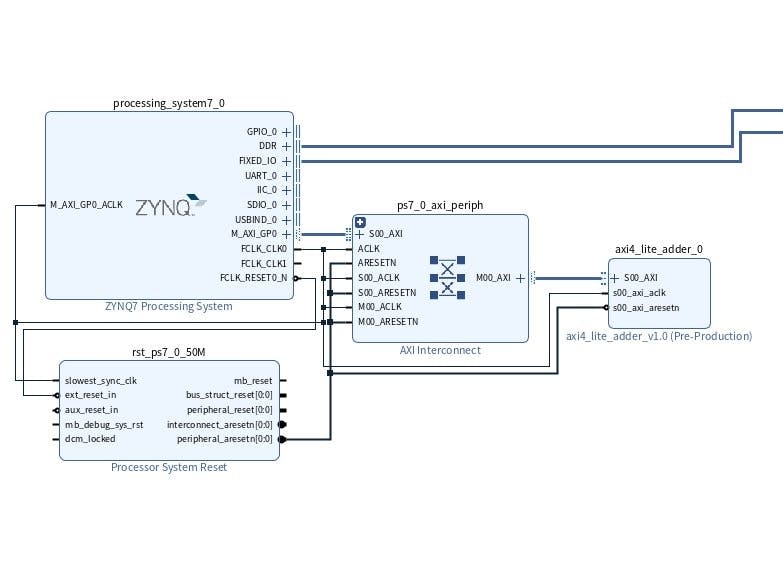

Leverage Built-In Ethernet on Zynq to Perform Memory Access Using AXI Manager - MATLAB & Simulink Example - MathWorks France